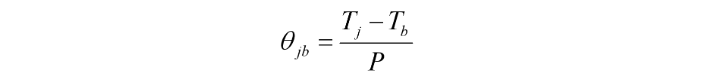

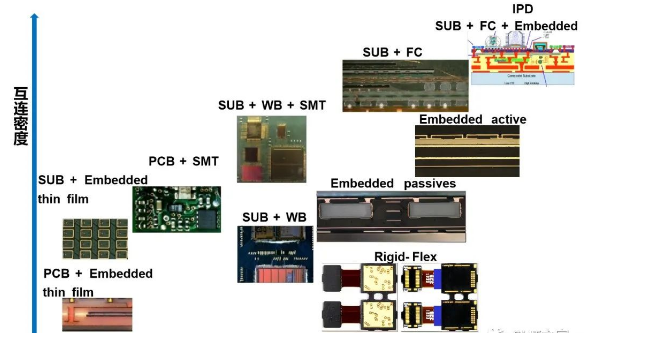

PCBA互联密度发展时间轴:

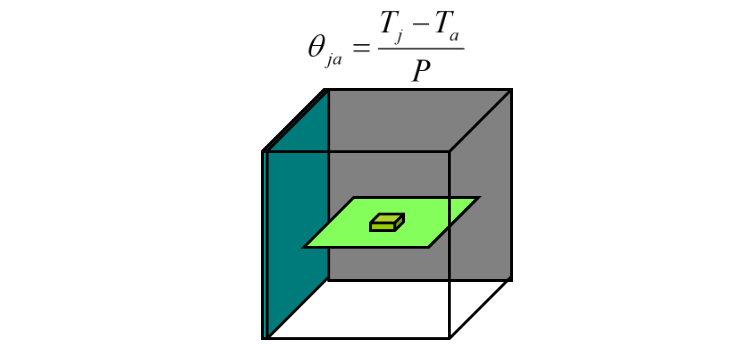

qja

qjma

a.空气流速范围为 0-1000 LFM

b.定义标准由文件 JESD51-6给出

c.Ta = 空气温度,取点为风洞上流温度

d.印制板朝向为重大影响因素

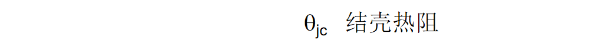

qjc

a.从结点到封装外表面(壳)的热阻,外表面壳取点尽量靠近Die安装区域

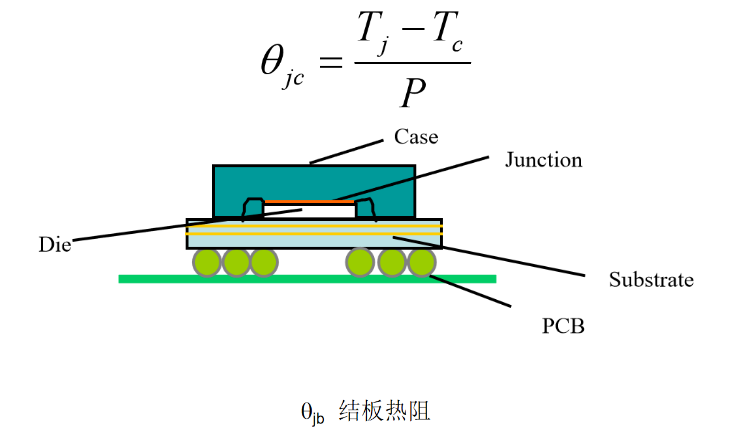

严格地讲,Theta-JB不仅仅反映了芯片的内热阻,同时也反映了部分环境热阻,如印制板。正因如此,

Theta-JB相对于其它热阻而言,虽然JEDEC组织在99年就发布了它的热阻定义方式,但是芯片供应商

采用较慢。

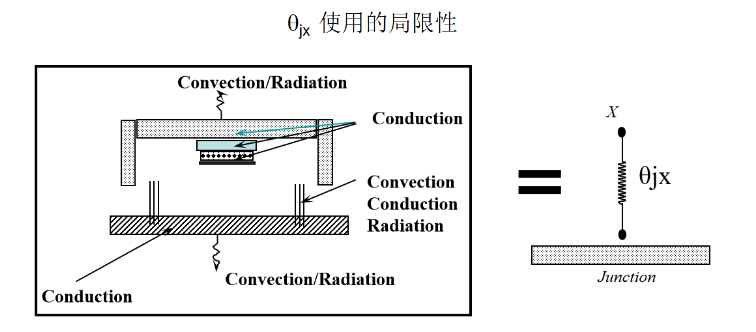

a.qjx 试图采用简单的热阻表示复杂的芯片传热现象

b.芯片内部的热传现象非常复杂,无法使用热阻来完美表示;

c.热阻qjx 无法用于准确预测芯片的温度,只能提供定性的热性能对比;

d.如需准确预测特定工况下芯片的温度,我们需要其它的方法

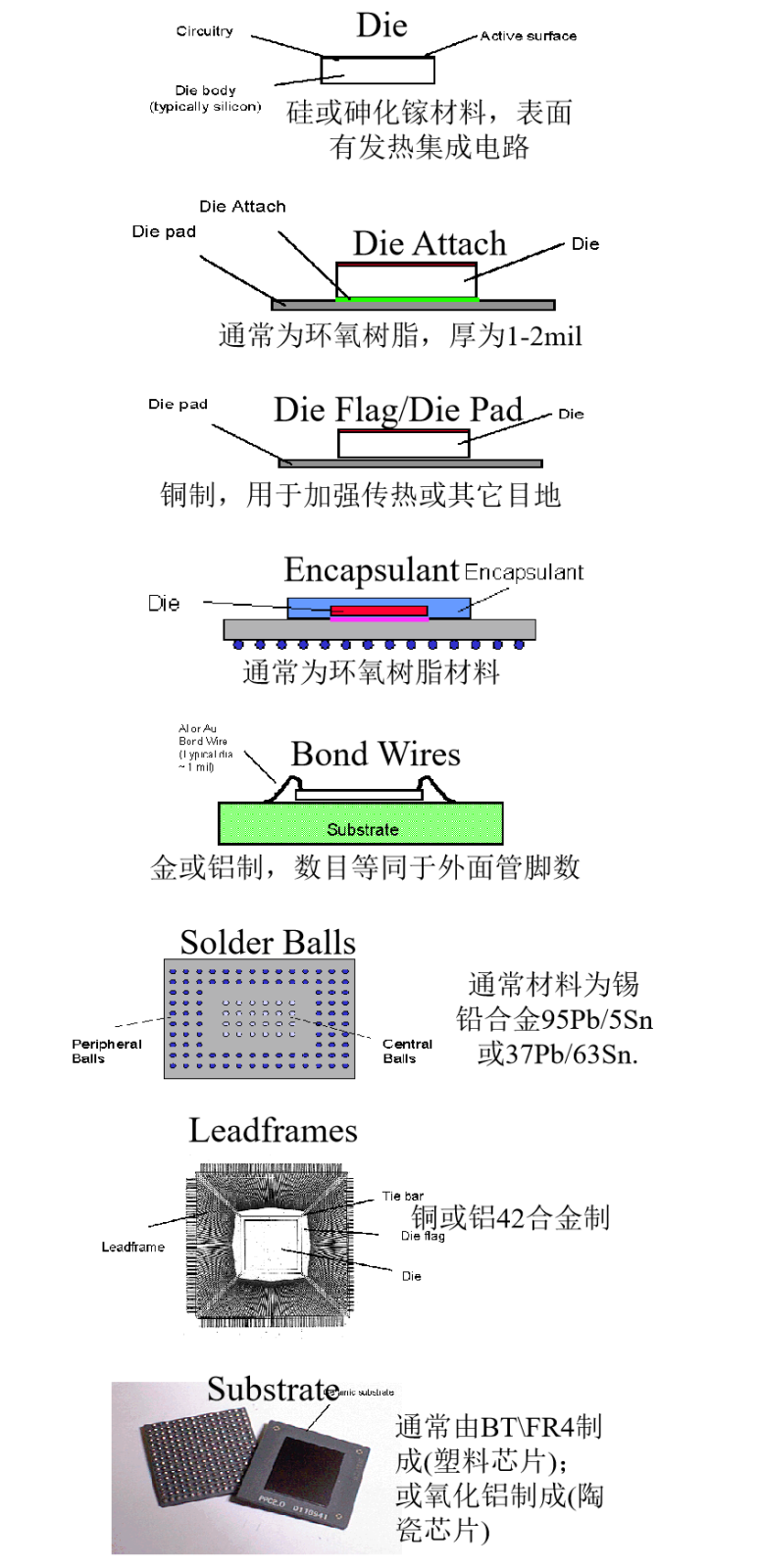

芯片的详细模型

建立所有芯片内部所有影响传热的结构

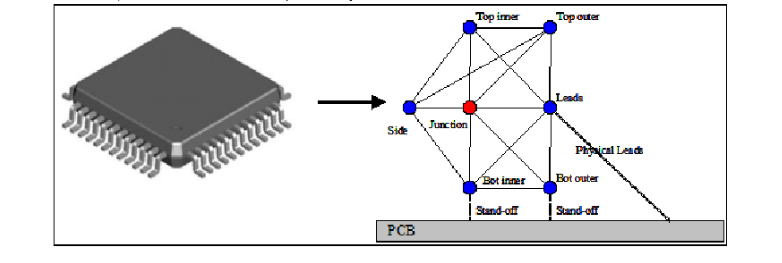

热阻网络模型-DELPHI模型

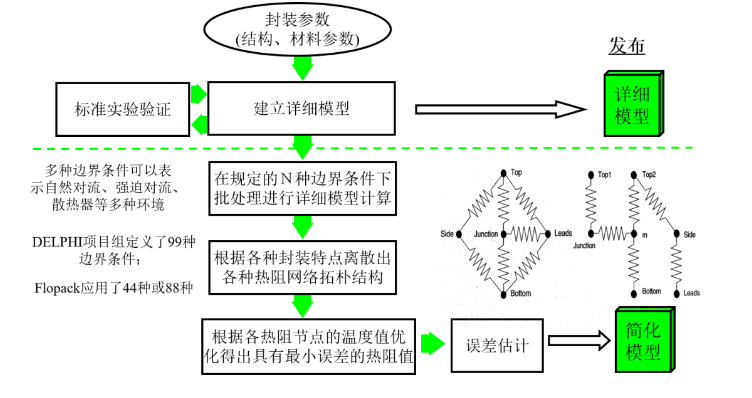

DELPHI 项目:从1993年到1996年,由欧盟资助,Flomerics公司负责协调,Alcatel Bell 、Alca

telEspace 、Philips CFT 、Thomson CSF 、Flomerics 、NMRC 等公司合作,旨在开发芯片的简化热

模型的精确表示方法。

PROFIT项目:同样由欧盟资助,由Philips公司负责协调,Flomerics、Nokia、Infineon、Philips、

ST、Micred、TIMA、等公司合作,旨在开发芯片热模型的快速建立方法。

项目产生了一系列成果,如芯片的热阻网络模型DELPHI标准、JEDEC组织认证的唯一热模型库FLO

PACK、芯片热应力分析工具Flo/stress等。

PROFIT 项目

PRediction OF temperature gradients Influencing The quality of electronic products

DELPHI项目

DEvelopment of Libraries of PHysical models for an Integrated design environment

DELPHI模型生成原理

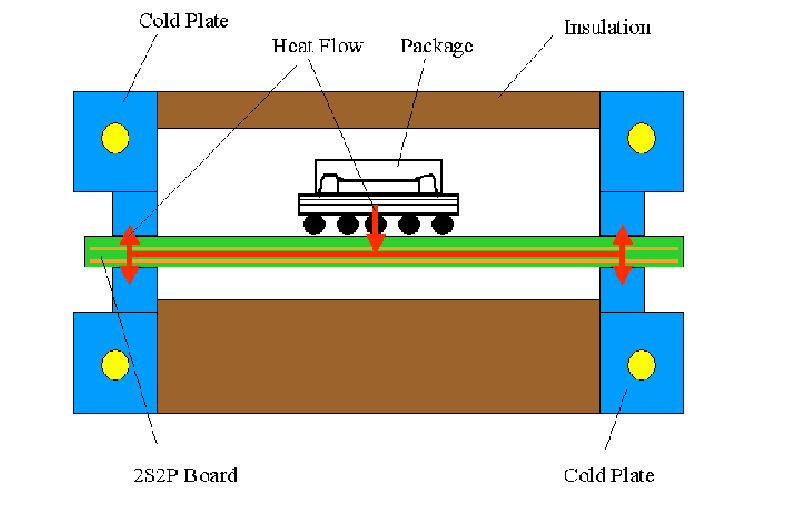

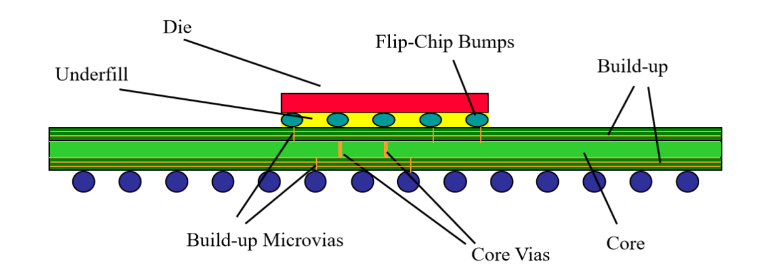

PBGA封装模型的建立

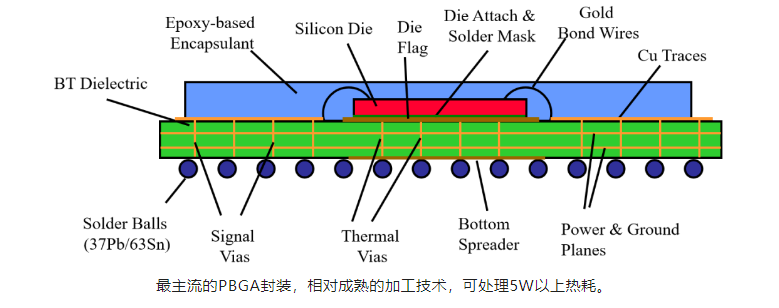

主要类型的PBGA封装

Wire-Bonded PBGA (Die-up)

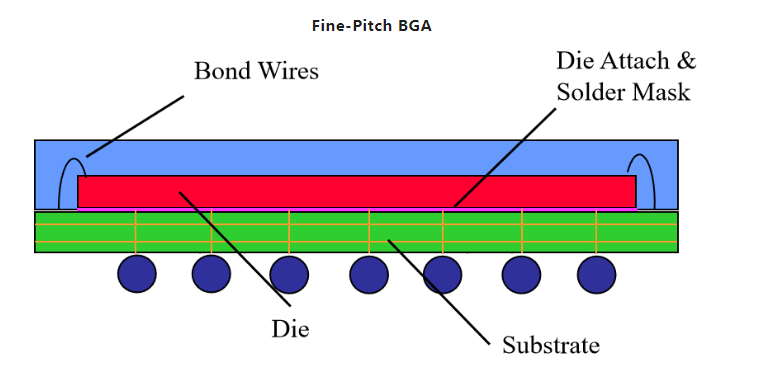

a.由die-up PBGA变化而来;

1.别名: FSBGA, ChipArrayTM;

2.焊球间隙较小;

3.可归类为 Near-CSP;

4.建模也较困难;

5.焊球间隙典型值为1mm,0.8mm,0.65mm,0.5mm,0.4mm;

6.经常缺少明显可见,比Die尺寸大的Die Pad,因为Die大小与封装大小相近;

7.基片(substrate)中每个信号过孔都必须单独建出;

8.在FLOPACK中,别名ChipArrayTM;

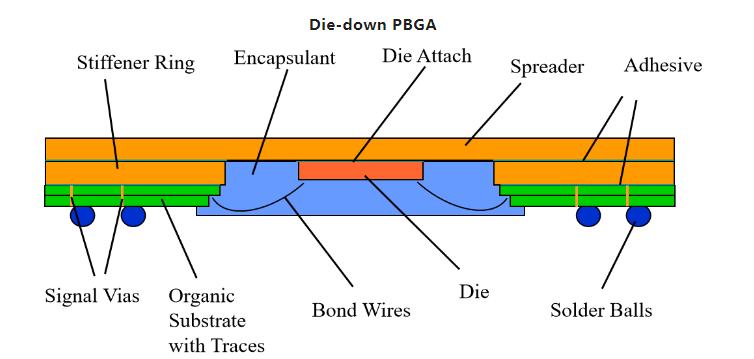

a.最常见的Die-down PBGA芯片为Amkor 公司的SuperBGATM ,但是SuperBGA中无上图结构中的加强环(Stiffener Ring)

b.Spreader(铜合金)可直接与散热器相连,良好的散热性能,可处理功耗8-10W

c.如无加强环(Stiffener Ring),则塑料基片与Spreader直接相连。

c.基片(substrate)复杂,一般中间层为BT层,两边另附有其它层。

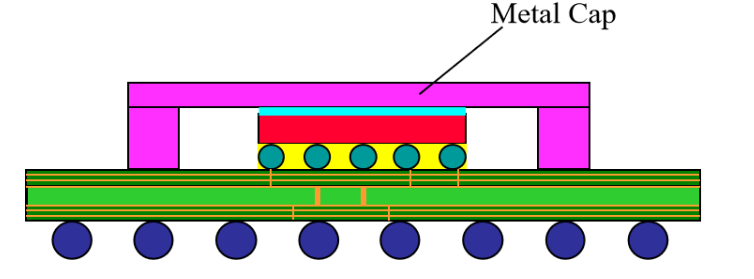

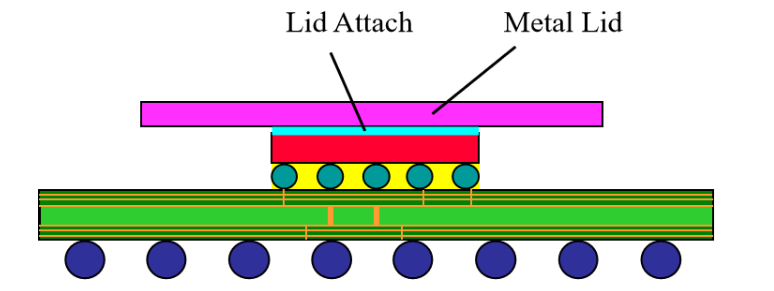

Metal Cap与Lid可能由铝与铜制

建模时需特别注意Cap/Lid Attach的厚度与材质,因为该类芯片功耗一般较大,主要热阻的组成部分之一Attach

即使有较小的误差,也会引起结温和热阻值Theta-JC估计较大的误差。

免责声明:本文系网络转载或改编,版权归原作者所有。但因转载众多,无法确认真正原始作者,故标明转载来源。如涉及版权等问题,

请与我们联系删除!本文内容为原作者观点,并不代表我司赞同其观点和对真实性负责。